Disclaimer: The postings on this site are my own and don't necessarily represent IBM's positions, strategies, or opinions.

"Is there a single greater thing you can teach an 8, 9, or 10-year old than to sail solo? Name me another activity that teaches geometry, mechanics, and physics while showing a small child that the mind always matters more than brute strength, and that size and gender are irrelevant to success. A sport where the playing field of wind and water mutates with every race to remind them that nature is ever-dynamic – yet enforces rules of right-of-way, sportsmanship, and marine safety. Lessons that train them to assemble complex sails and rigging, wash their own clothes, and not panic when capsizing. Lessons that teach them to trust their judgement, take responsibility for their decisions and not to blame anyone/anything else other than themselves. A lifestyle that begins with a love for the water, and ends with a wizard-like ability to read its secret language of waves, clouds, currents and the predictable movement of a boat. Sailing is a way of seeing the world -- without a digital screen" - Wesley Hsu

root@me ~ $ whoami

Some words about me

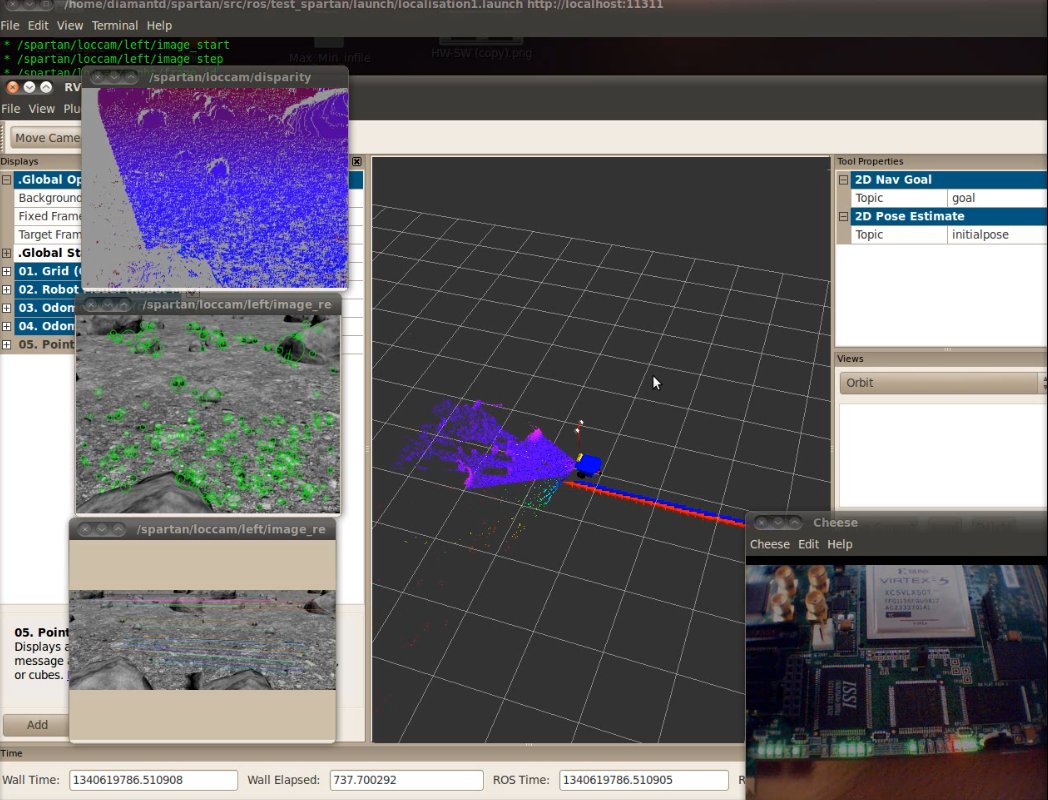

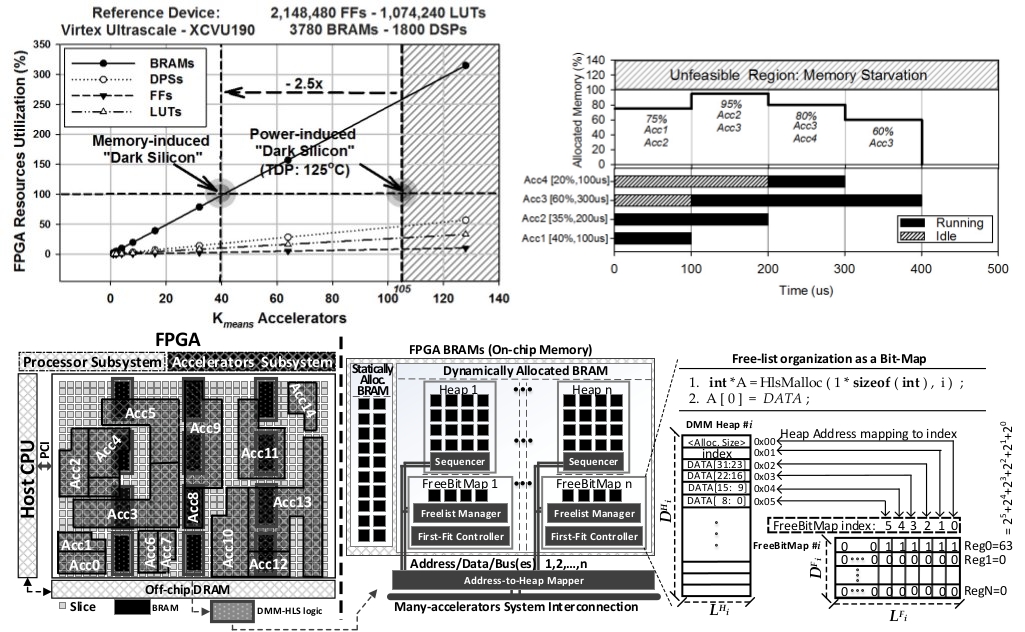

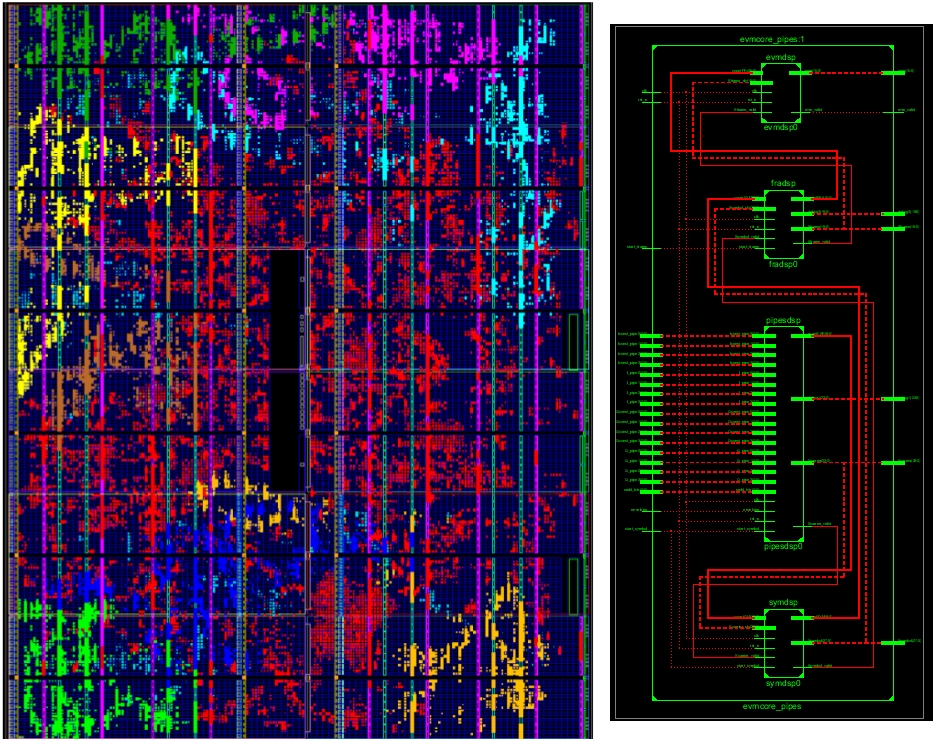

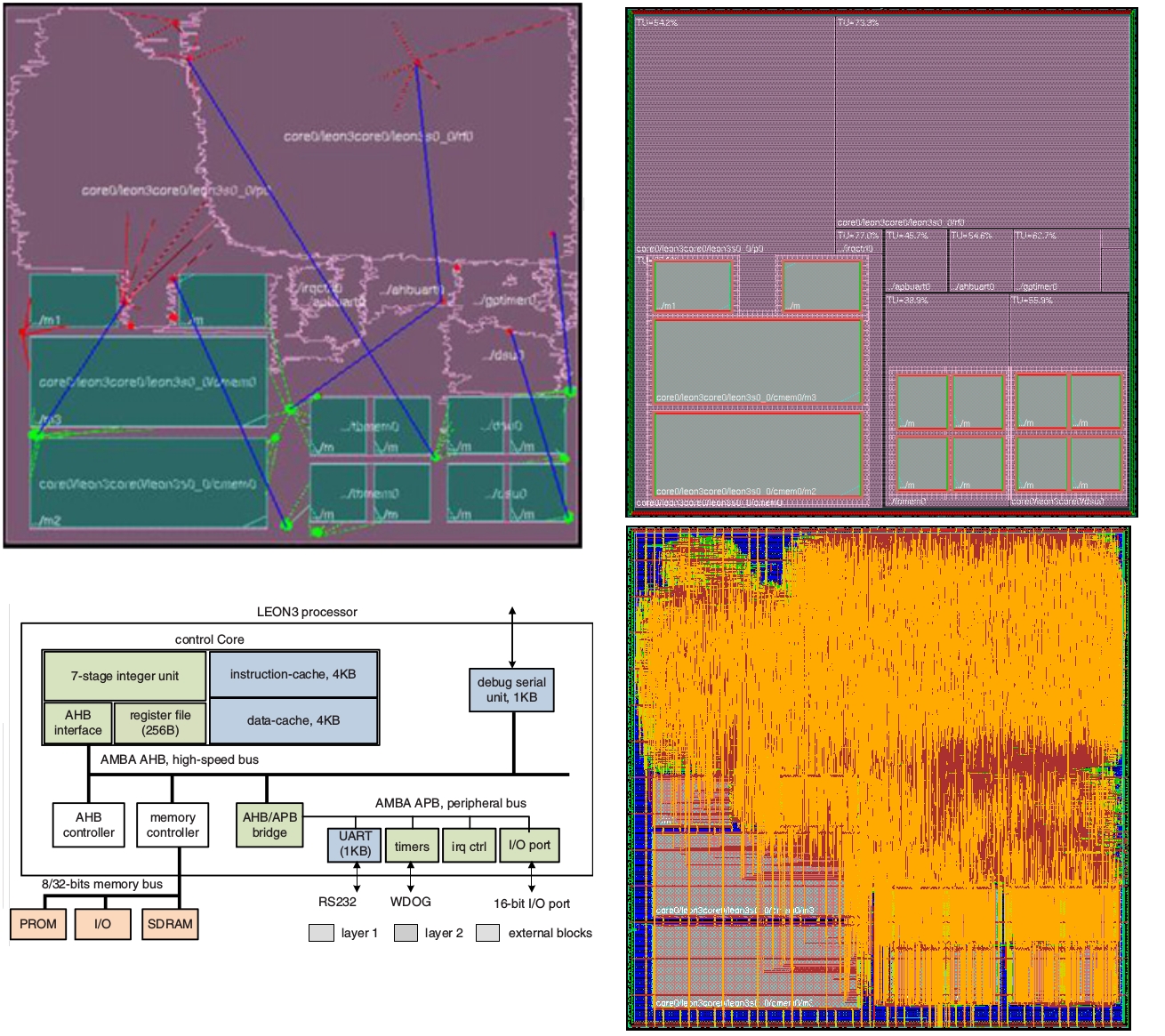

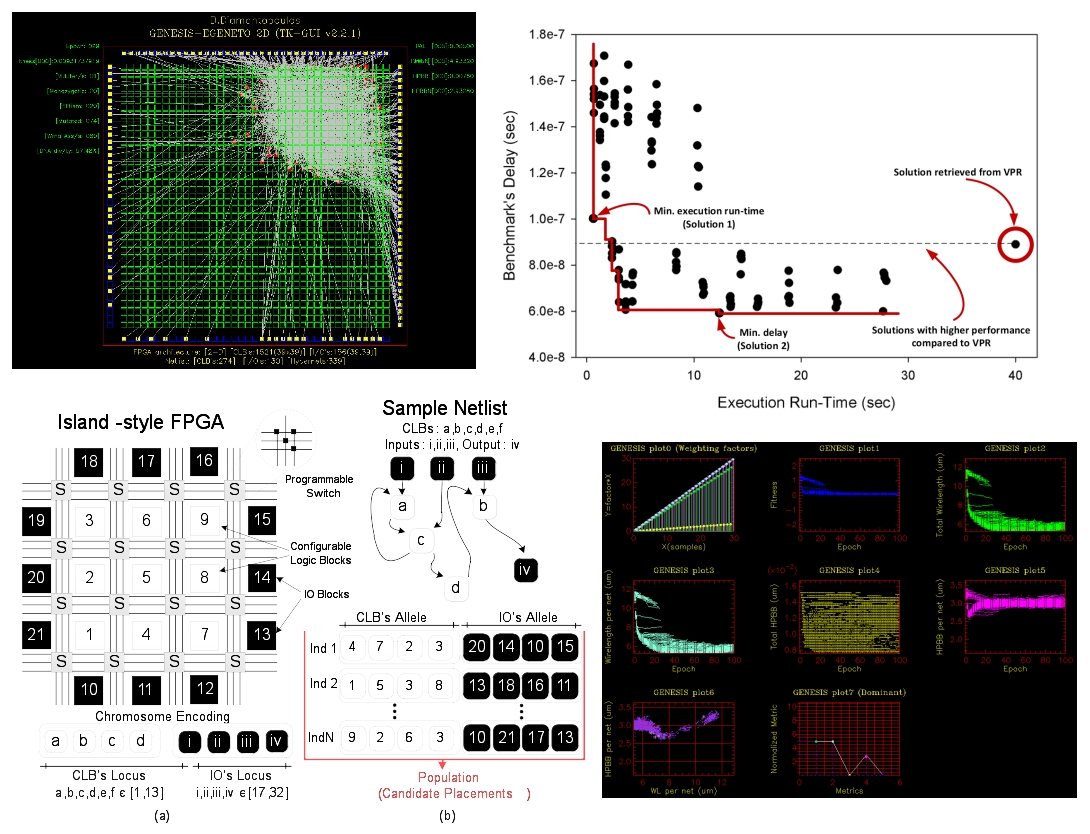

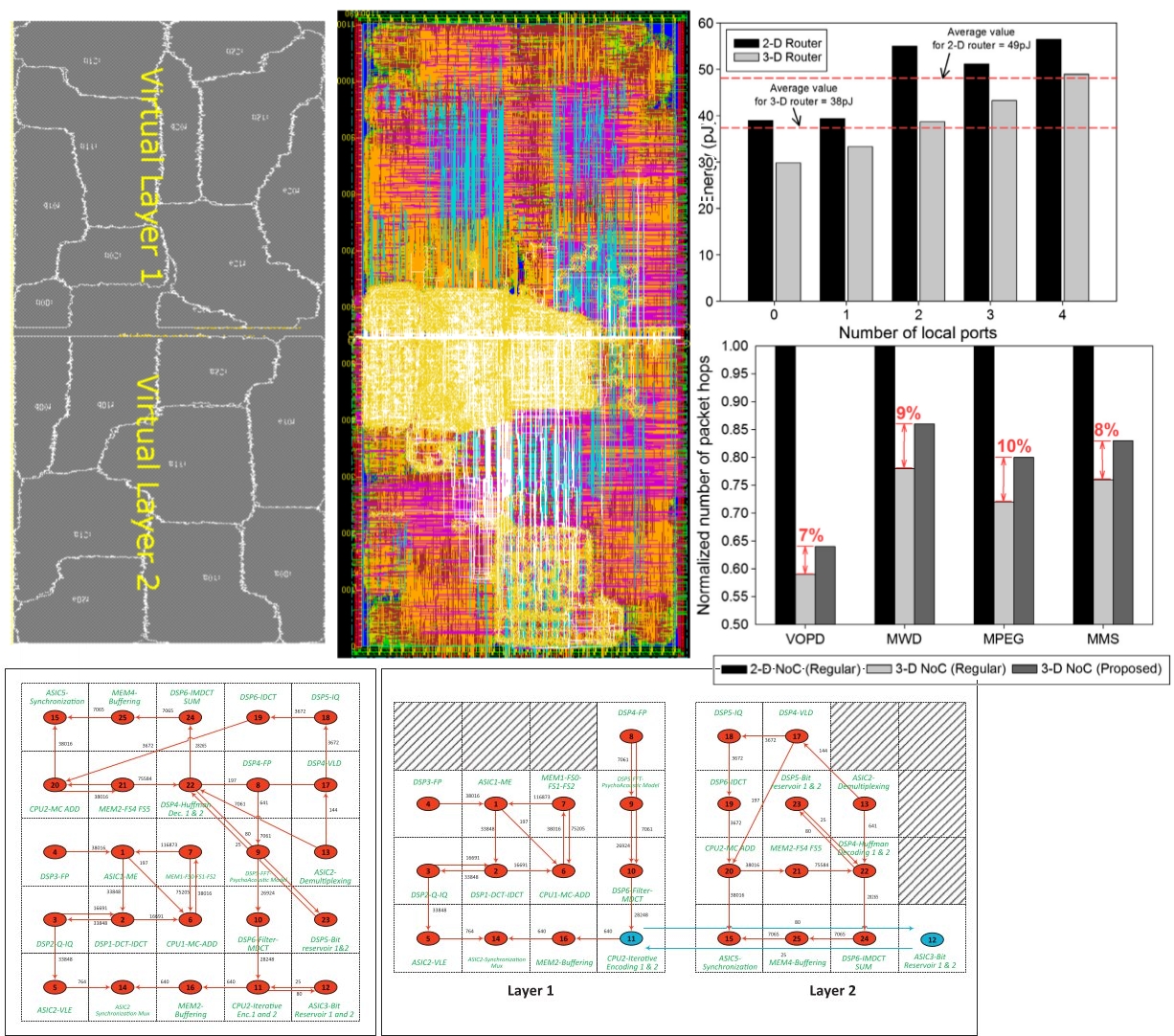

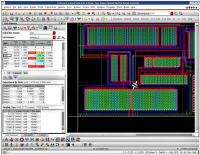

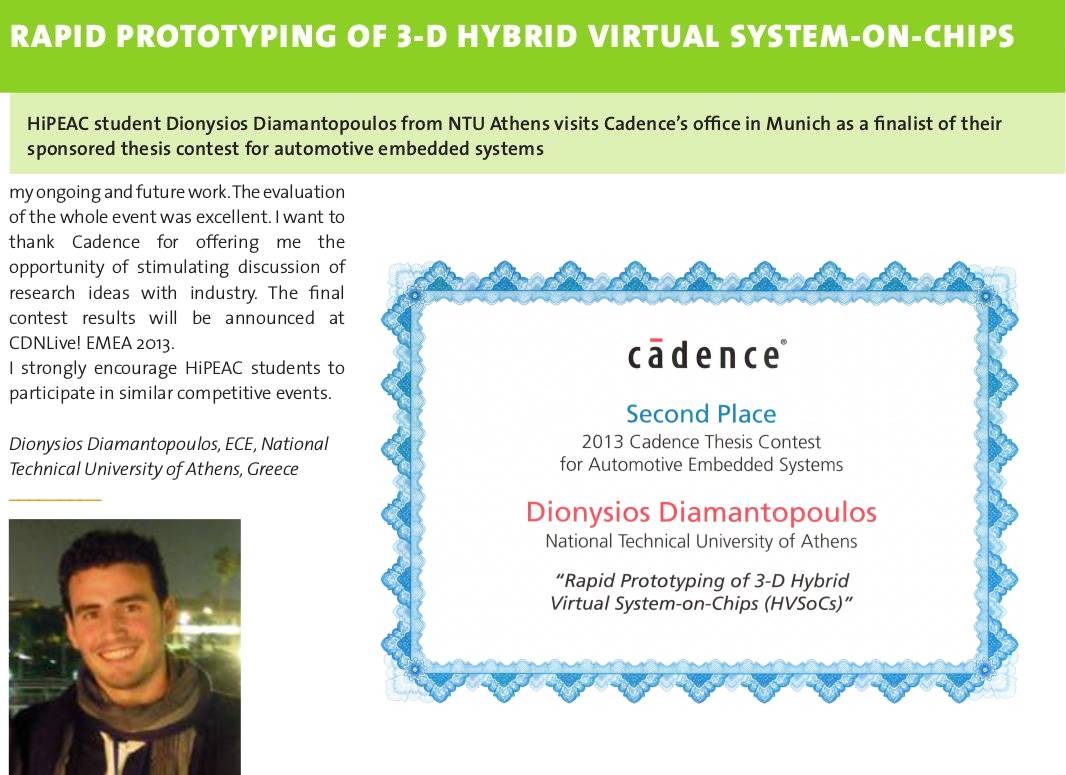

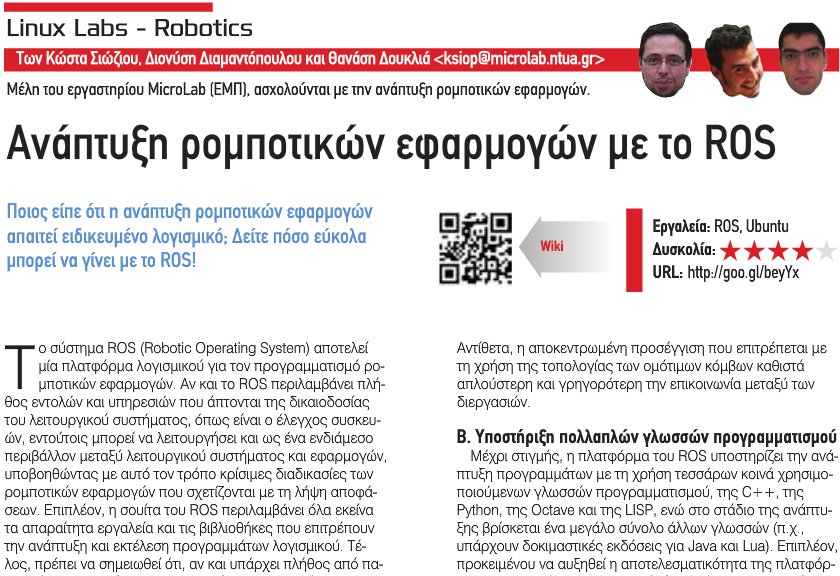

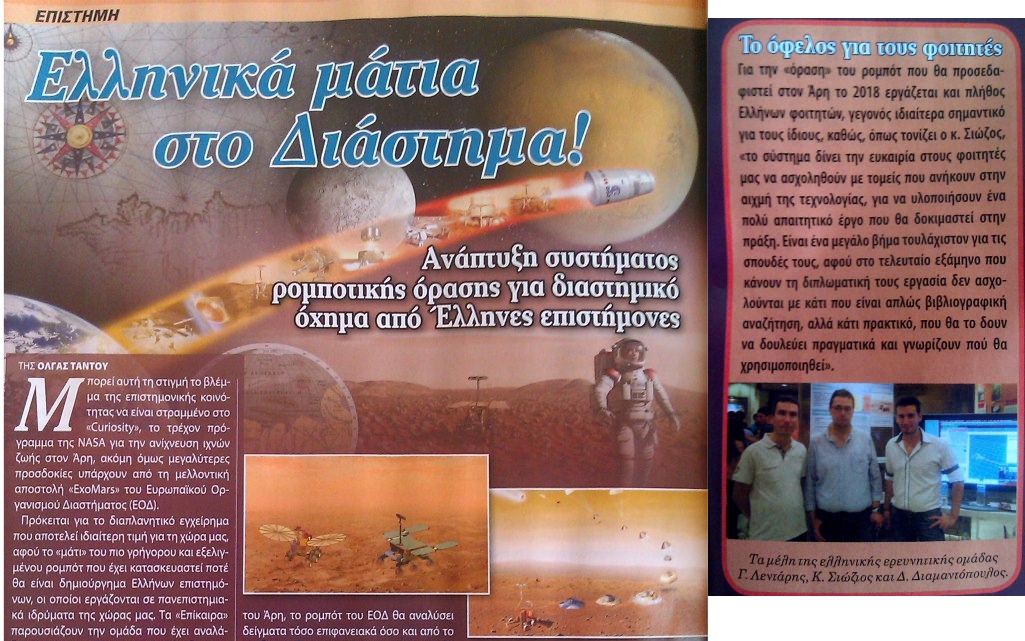

Developing innovative digital systems & design tools by following a multi-facet approach is my core belief in the last years of my work experience. A strong research background gives me the analytical framework for simplifying complexity. As a hands-on senior engineer I design efficient architectures that support real-world computing platforms. In the past years I have actively participated in several leading multi-national projects delivering world-class digital systems with highly acknowledged contribution in the realization of reconfigurable and application specific computing. Being passionate about all things to do with silicon bring-up, I am constantly looking to deploy my expertise in world-class engineering challenges. Currently, I am a Reasearch Scientist at the Cloud and AI Systems Research Department of IBM Research Europe - Zurich Laboratory. Previously I was a Post-Doc Reasearcher at the Heterogeneous Cognitive Computing Systems Group of the same department, researching novel architectures for energy-efficient FPGA accelerators, towards HPC, Big Data, and IoT applications (project FET-H2020 Open transPREcision COMPuting). Before joining IBM Research, I was a PhD researcher at Microlab-NTUA and a research associate at ICCS.

-

Insight - Passionate about all things to do with silicon bring-up.

-

Skills - Multi-disciplinary engineering profile & collaborative research focus.